Merge pull request #1 from stv0g/master

Updated board definition files for Vivado 2015.4

This commit is contained in:

commit

fd01c272b9

213 changed files with 303262 additions and 10 deletions

47

README.md

47

README.md

|

|

@ -1,19 +1,45 @@

|

|||

Various Files for MYiR ZTurn Board

|

||||

==================================

|

||||

# Various Files & Examples for MYiR Z-turn Board

|

||||

|

||||

Information

|

||||

-----------

|

||||

|

||||

|

||||

Contents:

|

||||

## Contents

|

||||

|

||||

- I/O constraints file (`constraints/`)

|

||||

- board definitions and autmation (`board-definition/`), drop in `Xilinx/Vivado/2014.4`

|

||||

This repository contains:

|

||||

|

||||

License

|

||||

-------

|

||||

1. I/O constraints file (`constraints/`)

|

||||

2. Board interface definition and autmation (`boards/`)

|

||||

3. KiCAD Pmod Adapter Board (`pmod-cape/`)

|

||||

4. SDSoC Platform definition (`sdsoc/`)

|

||||

5. Some simple Vivado examples (`examples/`)

|

||||

|

||||

Copyright (c) 2015, Sergiusz 'q3k' Bazański <q3k@q3k.org>

|

||||

## Installing

|

||||

|

||||

For instructions on how to install the board definition files, the following wiki page can be used.

|

||||

|

||||

https://reference.digilentinc.com/vivado:boardfiles2015

|

||||

|

||||

Alternatively, you can add the following line to your Vivado init script (`~/.Xilinx/Vivado/init.tcl`):

|

||||

|

||||

```tcl

|

||||

set_param board.repoPaths [list “<path_to_repo>/boards/board_files”]

|

||||

```

|

||||

|

||||

For a full description of the board definition XML schemas, please consult UG895, Appendix A *Board Interface File*.

|

||||

|

||||

## References & Links

|

||||

|

||||

* [Z-turn Product Page](http://www.myirtech.com/list.asp?id=502)

|

||||

* [Z-turn Manuals, Schematics & Example designs](https://rwth-aachen.sciebo.de/index.php/s/f030d08ff42ee4faefcd63dc32e104bc), [new version](https://rwth-aachen.sciebo.de/index.php/s/MCzrMyyzyvRlRce)

|

||||

* [Z-turn Wiki](https://wiki.hackerspace.pl/projects:zturn-hackers) (inofficial, Warsaw Hackerspace)

|

||||

* [Zynq Channel](irc://##zynq@irc.freenode.net): ##zynq on freenode.net (inofficial, [statistics](https://dev.0l.dn42/irc/zynq/), [webchat](http://webchat.freenode.net?channels=%23%23zynq))

|

||||

* [Adam Taylors Microzed Cronicles](http://git.io/vtRGd)

|

||||

|

||||

## License

|

||||

|

||||

- Copyright (c) 2015, Sergiusz 'q3k' Bazański <q3k@q3k.org>

|

||||

- Copyright (c) 2015-2016, Steffen 'stv0g' Vogel <stv0g@0l.de>

|

||||

|

||||

```

|

||||

All rights reserved.

|

||||

|

||||

Redistribution and use in source and binary forms, with or without modification, are permitted provided that the following conditions are met:

|

||||

|

|

@ -23,3 +49,4 @@ Redistribution and use in source and binary forms, with or without modification,

|

|||

2. Redistributions in binary form must reproduce the above copyright notice, this list of conditions and the following disclaimer in the documentation and/or other materials provided with the distribution.

|

||||

|

||||

THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT HOLDER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

|

||||

```

|

||||

|

|

|

|||

141

boards/board_files/zturn-7z010/2.1/board.xml

Normal file

141

boards/board_files/zturn-7z010/2.1/board.xml

Normal file

|

|

@ -0,0 +1,141 @@

|

|||

<?xml version="1.0" encoding="UTF-8" standalone="no" ?><!--

|

||||

################################################################################

|

||||

#

|

||||

# MYiR Z-turn Board Definition File

|

||||

#

|

||||

# Sergiusz 'q3k' Bazański <q3k@q3k.org>

|

||||

# Steffen 'stv0g' Vogel <stv0g@0l.de>

|

||||

#

|

||||

################################################################################-->

|

||||

|

||||

<board name="mys-7z010" schema_version="2.1" vendor="myir.com" display_name="Z-turn Board (MYS-7Z010-C)" url="http://www.myirtech.com/list.asp?id=502" preset_file="preset.xml">

|

||||

<images>

|

||||

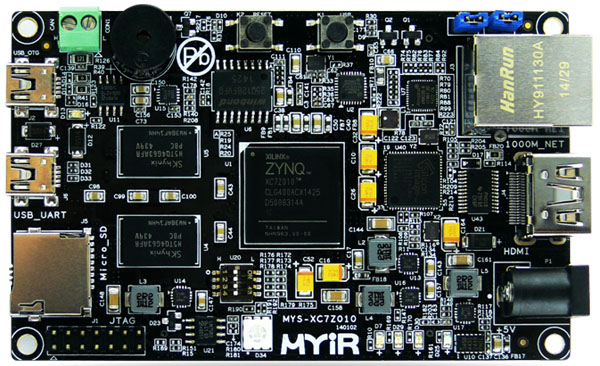

<image name="zturn_board.jpg" display_name="Z-turn Board" sub_type="board">

|

||||

<description>Z-turn Board top image</description>

|

||||

</image>

|

||||

</images>

|

||||

<description>The Z-turn board is a cheap Zynq evaluation board from the Chinese company MYiR Technologies.</description>

|

||||

<file_version>2.1</file_version>

|

||||

<compatible_board_revisions>

|

||||

<revision id="0">4</revision>

|

||||

</compatible_board_revisions>

|

||||

<components>

|

||||

<component name="part0" display_name="Z-turn Board" type="fpga" part_name="xc7z010clg400-1" pin_map_file="part0_pins.xml" vendor="xilinx" spec_url="http://www.myirtech.com/list.asp?id=502">

|

||||

<description>FPGA part on the board</description>

|

||||

<interfaces>

|

||||

<interface name="ps7_fixedio" mode="master" type="xilinx.com:display_processing_system7:fixedio_rtl:1.0" of_component="ps7_fixedio" preset_proc="ps7_preset" />

|

||||

<interface name="rgb_led" mode="master" type="xilinx.com:interface:gpio_rtl:1.0" of_component="rgb_led" preset_proc="rgb_led_preset">

|

||||

<preferred_ips>

|

||||

<preferred_ip name="axi_gpio" vendor="xilinx.com" library="ip" order="0" />

|

||||

</preferred_ips>

|

||||

<port_maps>

|

||||

<port_map logical_port="TRI_O" physical_port="rgb_led_tri_o" dir="out" left="2" right="0">

|

||||

<pin_maps>

|

||||

<pin_map port_index="0" component_pin="rgb_led_tri_o_0" />

|

||||

<pin_map port_index="1" component_pin="rgb_led_tri_o_1" />

|

||||

<pin_map port_index="2" component_pin="rgb_led_tri_o_2" />

|

||||

</pin_maps>

|

||||

</port_map>

|

||||

</port_maps>

|

||||

</interface>

|

||||

<interface name="buzzer" mode="master" type="xilinx.com:interface:gpio_rtl:1.0" of_component="buzzer" preset_proc="buzzer_preset">

|

||||

<preferred_ips>

|

||||

<preferred_ip name="axi_gpio" vendor="xilinx.com" library="ip" order="0" />

|

||||

</preferred_ips>

|

||||

<port_maps>

|

||||

<port_map logical_port="TRI_O" physical_port="buzzer_tri_o" dir="out">

|

||||

<pin_maps>

|

||||

<pin_map port_index="0" component_pin="buzzer_tri_o_0" />

|

||||

</pin_maps>

|

||||

</port_map>

|

||||

</port_maps>

|

||||

</interface>

|

||||

<interface name="sws_4bits" mode="master" type="xilinx.com:interface:gpio_rtl:1.0" of_component="sws_4bits" preset_proc="sws_4bits_preset">

|

||||

<preferred_ips>

|

||||

<preferred_ip vendor="xilinx.com" library="ip" name="axi_gpio" order="0" />

|

||||

</preferred_ips>

|

||||

<port_maps>

|

||||

<port_map logical_port="TRI_I" physical_port="sws_4bits_tri_i" dir="in" left="3" right="0">

|

||||

<pin_maps>

|

||||

<pin_map port_index="0" component_pin="sws_4bits_tri_i_0" />

|

||||

<pin_map port_index="1" component_pin="sws_4bits_tri_i_1" />

|

||||

<pin_map port_index="2" component_pin="sws_4bits_tri_i_2" />

|

||||

<pin_map port_index="3" component_pin="sws_4bits_tri_i_3" />

|

||||

</pin_maps>

|

||||

</port_map>

|

||||

</port_maps>

|

||||

</interface>

|

||||

<interface mode="master" name="i2c0" type="xilinx.com:interface:iic_rtl:1.0" of_component="i2c0">

|

||||

<description>I2C Interface for onboard G-rate and temperature sensors</description>

|

||||

<preferred_ips>

|

||||

<preferred_ip vendor="xilinx.com" library="ip" name="axi_iic" order="0" />

|

||||

</preferred_ips>

|

||||

<port_maps>

|

||||

<port_map logical_port="SDA_I" physical_port="i2c0_sda_i" dir="in">

|

||||

<pin_maps>

|

||||

<pin_map port_index="0" component_pin="i2c0_sda_i" />

|

||||

</pin_maps>

|

||||

</port_map>

|

||||

<port_map logical_port="SDA_O" physical_port="i2c0_sda_o" dir="out">

|

||||

<pin_maps>

|

||||

<pin_map port_index="0" component_pin="i2c0_sda_i" />

|

||||

</pin_maps>

|

||||

</port_map>

|

||||

<port_map logical_port="SDA_T" physical_port="i2c0_sda_t" dir="out">

|

||||

<pin_maps>

|

||||

<pin_map port_index="0" component_pin="i2c0_sda_i" />

|

||||

</pin_maps>

|

||||

</port_map>

|

||||

<port_map logical_port="SCL_I" physical_port="i2c0_scl_i" dir="in">

|

||||

<pin_maps>

|

||||

<pin_map port_index="0" component_pin="i2c0_scl_i" />

|

||||

</pin_maps>

|

||||

</port_map>

|

||||

<port_map logical_port="SCL_O" physical_port="i2c0_scl_o" dir="out">

|

||||

<pin_maps>

|

||||

<pin_map port_index="0" component_pin="i2c0_scl_i" />

|

||||

</pin_maps>

|

||||

</port_map>

|

||||

<port_map logical_port="SCL_T" physical_port="i2c0_scl_t" dir="out">

|

||||

<pin_maps>

|

||||

<pin_map port_index="0" component_pin="i2c0_scl_i" />

|

||||

</pin_maps>

|

||||

</port_map>

|

||||

</port_maps>

|

||||

</interface>

|

||||

</interfaces>

|

||||

</component>

|

||||

<component name="ps7_fixedio" display_name="PS7 fixed IO" type="chip" sub_type="fixed_io" major_group="" />

|

||||

<component name="buzzer" display_name="Piezo Buzzer" type="chip" sub_type="led" major_group="General Purpose Input or Output">

|

||||

<description>Piezo Buzzer on Board (Schematic: M1)</description>

|

||||

</component>

|

||||

<component name="rgb_led" display_name="RGB LED" type="chip" sub_type="led" major_group="General Purpose Input or Output">

|

||||

<description>RGB LED, 2 to 0, Active Low (Schematic: D34)</description>

|

||||

</component>

|

||||

<component name="sws_4bits" display_name="DIP switches" type="chip" sub_type="switch" major_group="General Purpose Input or Output">

|

||||

<description>DIP Switches, 3 to 0 (Schematic: U20)</description>

|

||||

</component>

|

||||

<component name="i2c0" display_name="IIC" type="chip" sub_type="mux" major_group="Miscellaneous">

|

||||

<description>I2C Bus 0 wired to PL</description>

|

||||

</component>

|

||||

</components>

|

||||

<jtag_chains>

|

||||

<jtag_chain name="chain1">

|

||||

<position name="0" component="part0" />

|

||||

</jtag_chain>

|

||||

</jtag_chains>

|

||||

<connections>

|

||||

<connection name="part0_rgb_led" component1="part0" component2="rgb_led">

|

||||

<connection_map name="part0_rgb_led_1" c1_st_index="4" c1_end_index="6" c2_st_index="0" c2_end_index="2" />

|

||||

</connection>

|

||||

<connection name="part0_sws_4bits" component1="part0" component2="sws_4bits">

|

||||

<connection_map name="part0_sws_4bits_1" c1_st_index="0" c1_end_index="3" c2_st_index="0" c2_end_index="3" />

|

||||

</connection>

|

||||

<connection name="part0_buzzer" component1="part0" component2="buzzer">

|

||||

<connection_map name="part0_buzzer_1" c1_st_index="7" c1_end_index="7" c2_st_index="0" c2_end_index="0" />

|

||||

</connection>

|

||||

<connection name="part0_i2c0" component1="part0" component2="i2c0">

|

||||

<connection_map name="part0_i2c0_1" c1_st_index="8" c1_end_index="9" c2_st_index="0" c2_end_index="1" />

|

||||

</connection>

|

||||

</connections>

|

||||

</board>

|

||||

26

boards/board_files/zturn-7z010/2.1/part0_pins.xml

Normal file

26

boards/board_files/zturn-7z010/2.1/part0_pins.xml

Normal file

|

|

@ -0,0 +1,26 @@

|

|||

<?xml version="1.0" encoding="UTF-8" standalone="no"?><!--

|

||||

################################################################################

|

||||

#

|

||||

# MYiR Z-turn FPGA Pin Definition File

|

||||

#

|

||||

# Sergiusz 'q3k' Bazański <q3k@q3k.org>

|

||||

# Steffen 'stv0g' Vogel <stv0g@0l.de>

|

||||

#

|

||||

################################################################################-->

|

||||

|

||||

<part_info part_name="xc7z010clg400-1">

|

||||

<pins>

|

||||

<pin index="0" name="sws_4bits_tri_i_0" iostandard="LVCMOS33" loc="R19" /><!-- IO_B34_0 -->

|

||||

<pin index="1" name="sws_4bits_tri_i_1" iostandard="LVCMOS33" loc="T19" /><!-- IO_B34_25 -->

|

||||

<pin index="2" name="sws_4bits_tri_i_2" iostandard="LVCMOS33" loc="G14" /><!-- IO_B35_0 -->

|

||||

<pin index="3" name="sws_4bits_tri_i_3" iostandard="LVCMOS33" loc="J15" /><!-- IO_B35_25 -->

|

||||

<pin index="4" name="rgb_led_tri_o_0" iostandard="LVCMOS33" loc="R14" /><!-- IO_B34_LN6 -->

|

||||

<pin index="5" name="rgb_led_tri_o_1" iostandard="LVCMOS33" loc="Y16" /><!-- IO_B34_LP7 -->

|

||||

<pin index="6" name="rgb_led_tri_o_2" iostandard="LVCMOS33" loc="Y17" /><!-- IO_B34_LN7 -->

|

||||

<pin index="7" name="buzzer_tri_o_0" iostandard="LVCMOS33" loc="P18" /><!-- BP -->

|

||||

<pin index="8" name ="i2c0_scl_i" iostandard="LVCMOS33" loc="P16" /><!-- I2C0_SCL -->

|

||||

<pin index="9" name ="i2c0_sda_i" iostandard="LVCMOS33" loc="P15" /><!-- I2C0_SDA -->

|

||||

<pin index="10" name="mems_temp_intn" iostandard="LVCMOS33" loc="N17" /><!-- MEMS_INTn (wired-or for LM75 and Sil902x)-->

|

||||

<pin index="11" name="hdmi_int" iostandard="LVCMOS33" loc="W19" /><!-- HDMI_INT -->

|

||||

</pins>

|

||||

</part_info>

|

||||

324

boards/board_files/zturn-7z010/2.1/preset.xml

Normal file

324

boards/board_files/zturn-7z010/2.1/preset.xml

Normal file

|

|

@ -0,0 +1,324 @@

|

|||

<?xml version="1.0" encoding="UTF-8" standalone="no" ?><!--

|

||||

################################################################################

|

||||

#

|

||||

# MYiR Z-turn Board IP Presets

|

||||

#

|

||||

# Sergiusz 'q3k' Bazański <q3k@q3k.org>

|

||||

# Steffen 'stv0g' Vogel <stv0g@0l.de>

|

||||

#

|

||||

################################################################################-->

|

||||

|

||||

<ip_presets schema="1.0">

|

||||

<ip_preset preset_proc_name="ps7_preset">

|

||||

<ip vendor="xilinx.com" library="ip" name="processing_system7" version="*">

|

||||

<user_parameters>

|

||||

<!--########################################################################

|

||||

# PS Bank Voltage, Busses, Clocks

|

||||

########################################################################-->

|

||||

<user_parameter name="CONFIG.PCW_PRESET_BANK0_VOLTAGE" value="LVCMOS 3.3V" />

|

||||

<user_parameter name="CONFIG.PCW_PRESET_BANK1_VOLTAGE" value="LVCMOS 1.8V" />

|

||||

<user_parameter name="CONFIG.PCW_PACKAGE_NAME" value="clg400" />

|

||||

<user_parameter name="CONFIG.PCW_USE_M_AXI_GP0" value="1" />

|

||||

<user_parameter name="CONFIG.PCW_USE_M_AXI_GP1" value="0" />

|

||||

<user_parameter name="CONFIG.PCW_CRYSTAL_PERIPHERAL_FREQMHZ" value="33.333333" />

|

||||

<user_parameter name="CONFIG.PCW_ARMPLL_CTRL_FBDIV" value="40" />

|

||||

<user_parameter name="CONFIG.PCW_APU_CLK_RATIO_ENABLE" value="6:2:1" />

|

||||

<user_parameter name="CONFIG.PCW_CPU_PERIPHERAL_CLKSRC" value="ARM PLL" />

|

||||

<user_parameter name="CONFIG.PCW_DDR_PERIPHERAL_CLKSRC" value="DDR PLL" />

|

||||

<user_parameter name="CONFIG.PCW_QSPI_PERIPHERAL_CLKSRC" value="IO PLL" />

|

||||

<user_parameter name="CONFIG.PCW_ENET0_PERIPHERAL_CLKSRC" value="ARM PLL" />

|

||||

<user_parameter name="CONFIG.PCW_SDIO_PERIPHERAL_CLKSRC" value="IO PLL" />

|

||||

<user_parameter name="CONFIG.PCW_UART_PERIPHERAL_CLKSRC" value="IO PLL" />

|

||||

<user_parameter name="CONFIG.PCW_TTC0_CLK0_PERIPHERAL_CLKSRC" value="CPU_1X" />

|

||||

<user_parameter name="CONFIG.PCW_TTC0_CLK1_PERIPHERAL_CLKSRC" value="CPU_1X" />

|

||||

<user_parameter name="CONFIG.PCW_TTC0_CLK2_PERIPHERAL_CLKSRC" value="CPU_1X" />

|

||||

<user_parameter name="CONFIG.PCW_APU_PERIPHERAL_FREQMHZ" value="666.666666" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_ACT_DDR_FREQ_MHZ" value="533.333333" />

|

||||

<user_parameter name="CONFIG.PCW_ENET0_PERIPHERAL_FREQMHZ" value="1000 Mbps" />

|

||||

<user_parameter name="CONFIG.PCW_SDIO_PERIPHERAL_FREQMHZ" value="100" />

|

||||

<user_parameter name="CONFIG.PCW_QSPI_PERIPHERAL_FREQMHZ" value="200.000000" />

|

||||

<user_parameter name="CONFIG.PCW_UART_PERIPHERAL_FREQMHZ" value="100" />

|

||||

<user_parameter name="CONFIG.PCW_USB0_PERIPHERAL_FREQMHZ" value="60" />

|

||||

<user_parameter name="CONFIG.PCW_TTC0_CLK0_PERIPHERAL_FREQMHZ" value="133.333333" />

|

||||

<user_parameter name="CONFIG.PCW_TTC0_CLK1_PERIPHERAL_FREQMHZ" value="133.333333" />

|

||||

<user_parameter name="CONFIG.PCW_TTC0_CLK2_PERIPHERAL_FREQMHZ" value="133.333333" />

|

||||

|

||||

<!--########################################################################

|

||||

# Fabric Clocks - CLK0 enabled, CLK[3:1] disabled by default

|

||||

########################################################################-->

|

||||

<user_parameter name="CONFIG.PCW_FCLK0_PERIPHERAL_CLKSRC" value="IO PLL" />

|

||||

<user_parameter name="CONFIG.PCW_FCLK1_PERIPHERAL_CLKSRC" value="IO PLL" />

|

||||

<user_parameter name="CONFIG.PCW_FCLK2_PERIPHERAL_CLKSRC" value="IO PLL" />

|

||||

<user_parameter name="CONFIG.PCW_FCLK3_PERIPHERAL_CLKSRC" value="IO PLL" />

|

||||

<user_parameter name="CONFIG.PCW_FCLK_CLK0_BUF" value="true" />

|

||||

<user_parameter name="CONFIG.PCW_FCLK_CLK1_BUF" value="true" />

|

||||

<user_parameter name="CONFIG.PCW_FCLK_CLK2_BUF" value="false" />

|

||||

<user_parameter name="CONFIG.PCW_FCLK_CLK3_BUF" value="false" />

|

||||

<user_parameter name="CONFIG.PCW_FPGA0_PERIPHERAL_FREQMHZ" value="100" />

|

||||

<user_parameter name="CONFIG.PCW_FPGA1_PERIPHERAL_FREQMHZ" value="50" />

|

||||

<user_parameter name="CONFIG.PCW_FPGA2_PERIPHERAL_FREQMHZ" value="50" />

|

||||

<user_parameter name="CONFIG.PCW_FPGA3_PERIPHERAL_FREQMHZ" value="50" />

|

||||

<user_parameter name="CONFIG.PCW_EN_CLK0_PORT" value="1" />

|

||||

<user_parameter name="CONFIG.PCW_EN_CLK1_PORT" value="1" />

|

||||

<user_parameter name="CONFIG.PCW_EN_CLK2_PORT" value="0" />

|

||||

<user_parameter name="CONFIG.PCW_EN_CLK3_PORT" value="0" />

|

||||

<user_parameter name="CONFIG.PCW_EN_RST0_PORT" value="1" />

|

||||

<user_parameter name="CONFIG.PCW_EN_RST1_PORT" value="0" />

|

||||

<user_parameter name="CONFIG.PCW_EN_RST2_PORT" value="0" />

|

||||

<user_parameter name="CONFIG.PCW_EN_RST3_PORT" value="0" />

|

||||

|

||||

<!--########################################################################

|

||||

# DDR3

|

||||

########################################################################-->

|

||||

<user_parameter name="CONFIG.PCW_EN_DDR" value="1" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_PARTNO" value="MT41J256M16 RE-125" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_DEVICE_CAPACITY" value="4096 MBits" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_T_FAW" value="40.0" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_T_RC" value="48.91" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_CWL" value="6" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_DRAM_WIDTH" value="16 Bits" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_T_RAS_MIN" value="35.0" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_SPEED_BIN" value="DDR3_1066F" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_CLOCK_0_LENGTH_MM" value="0" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_CLOCK_1_LENGTH_MM" value="0" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_CLOCK_2_LENGTH_MM" value="0" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_CLOCK_3_LENGTH_MM" value="0" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_DQ_0_LENGTH_MM" value="0" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_DQ_1_LENGTH_MM" value="0" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_DQ_2_LENGTH_MM" value="0" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_DQ_3_LENGTH_MM" value="0" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_DQS_0_LENGTH_MM" value="0" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_DQS_1_LENGTH_MM" value="0" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_DQS_2_LENGTH_MM" value="0" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_DQS_3_LENGTH_MM" value="0" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_TRAIN_DATA_EYE" value="1" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_TRAIN_WRITE_LEVEL" value="1" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_TRAIN_READ_GATE" value="1" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_DQS_TO_CLK_DELAY_0" value="0.229" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_DQS_TO_CLK_DELAY_1" value="0.250" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_DQS_TO_CLK_DELAY_2" value="0.121" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_DQS_TO_CLK_DELAY_3" value="0.146" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_BOARD_DELAY0" value="0.271" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_BOARD_DELAY1" value="0.259" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_BOARD_DELAY2" value="0.219" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_BOARD_DELAY3" value="0.207" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_USE_INTERNAL_VREF" value="0" />

|

||||

|

||||

<!--########################################################################

|

||||

# Peripheral assignments

|

||||

########################################################################-->

|

||||

<user_parameter name="CONFIG.PCW_QSPI_GRP_SINGLE_SS_IO" value="MIO 1 .. 6" />

|

||||

<user_parameter name="CONFIG.PCW_USB0_RESET_IO" value="MIO 7" />

|

||||

<user_parameter name="CONFIG.PCW_QSPI_GRP_FBCLK_IO" value="MIO 8" />

|

||||

<user_parameter name="CONFIG.PCW_UART0_UART0_IO" value="MIO 10 .. 11" />

|

||||

<user_parameter name="CONFIG.PCW_I2C0_I2C0_IO" value="EMIO" />

|

||||

<user_parameter name="CONFIG.PCW_I2C1_I2C1_IO" value="MIO 12 .. 13" />

|

||||

<user_parameter name="CONFIG.PCW_CAN0_CAN0_IO" value="MIO 14 .. 15" />

|

||||

<user_parameter name="CONFIG.PCW_ENET0_ENET0_IO" value="MIO 16 .. 27" />

|

||||

<user_parameter name="CONFIG.PCW_USB0_USB0_IO" value="MIO 28 .. 39" />

|

||||

<user_parameter name="CONFIG.PCW_SD0_SD0_IO" value="MIO 40 .. 45" />

|

||||

<user_parameter name="CONFIG.PCW_SD0_GRP_CD_IO" value="MIO 46" />

|

||||

<user_parameter name="CONFIG.PCW_SD0_GRP_WP_IO" value="MIO 47" />

|

||||

<user_parameter name="CONFIG.PCW_UART1_UART1_IO" value="MIO 48 .. 49" />

|

||||

<user_parameter name="CONFIG.PCW_ENET0_GRP_MDIO_IO" value="MIO 52 .. 53" />

|

||||

<user_parameter name="CONFIG.PCW_TTC0_TTC0_IO" value="EMIO" />

|

||||

|

||||

<!--########################################################################

|

||||

# Enable Peripherals

|

||||

########################################################################-->

|

||||

<user_parameter name="CONFIG.PCW_QSPI_PERIPHERAL_ENABLE" value="1" />

|

||||

<user_parameter name="CONFIG.PCW_QSPI_GRP_FBCLK_ENABLE" value="1" />

|

||||

<user_parameter name="CONFIG.PCW_QSPI_GRP_SINGLE_SS_ENABLE" value="1" />

|

||||

<user_parameter name="CONFIG.PCW_USB0_PERIPHERAL_ENABLE" value="1" />

|

||||

<user_parameter name="CONFIG.PCW_ENET0_PERIPHERAL_ENABLE" value="1" />

|

||||

<user_parameter name="CONFIG.PCW_ENET0_GRP_MDIO_ENABLE" value="1" />

|

||||

<user_parameter name="CONFIG.PCW_SD0_PERIPHERAL_ENABLE" value="1" />

|

||||

<user_parameter name="CONFIG.PCW_SD0_GRP_CD_ENABLE" value="1" />

|

||||

<user_parameter name="CONFIG.PCW_SD0_GRP_WP_ENABLE" value="1" />

|

||||

<user_parameter name="CONFIG.PCW_CAN0_PERIPHERAL_ENABLE" value="1" />

|

||||

<user_parameter name="CONFIG.PCW_I2C0_PERIPHERAL_ENABLE" value="1" />

|

||||

<user_parameter name="CONFIG.PCW_I2C1_PERIPHERAL_ENABLE" value="1" />

|

||||

<user_parameter name="CONFIG.PCW_UART0_PERIPHERAL_ENABLE" value="1" />

|

||||

<user_parameter name="CONFIG.PCW_UART1_PERIPHERAL_ENABLE" value="1" />

|

||||

<user_parameter name="CONFIG.PCW_GPIO_PERIPHERAL_ENABLE" value="1" />

|

||||

<user_parameter name="CONFIG.PCW_GPIO_MIO_GPIO_ENABLE" value="1" />

|

||||

<user_parameter name="CONFIG.PCW_GPIO_EMIO_GPIO_ENABLE" value="0" />

|

||||

<user_parameter name="CONFIG.PCW_TTC0_PERIPHERAL_ENABLE" value="1" />

|

||||

|

||||

<!--########################################################################

|

||||

# Configure MIOs

|

||||

########################################################################-->

|

||||

<user_parameter name="CONFIG.PCW_MIO_0_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_1_PULLUP" value="disabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_2_PULLUP" value="disabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_3_PULLUP" value="disabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_4_PULLUP" value="disabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_5_PULLUP" value="disabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_6_PULLUP" value="disabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_7_PULLUP" value="disabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_8_PULLUP" value="disabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_9_PULLUP" value="disabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_10_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_11_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_12_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_13_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_14_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_15_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_16_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_17_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_18_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_19_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_20_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_21_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_22_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_23_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_24_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_25_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_26_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_27_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_28_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_29_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_30_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_31_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_32_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_33_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_34_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_35_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_36_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_37_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_38_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_39_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_40_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_41_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_42_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_43_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_44_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_45_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_46_PULLUP" value="disabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_47_PULLUP" value="disabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_48_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_49_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_50_PULLUP" value="disabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_51_PULLUP" value="disabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_52_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_53_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_0_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_1_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_2_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_3_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_4_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_5_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_6_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_7_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_8_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_9_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_10_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_11_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_12_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_13_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_14_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_15_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_16_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_17_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_18_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_19_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_20_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_21_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_22_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_23_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_24_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_25_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_26_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_27_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_28_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_29_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_30_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_31_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_32_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_33_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_34_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_35_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_36_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_37_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_38_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_39_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_40_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_41_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_42_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_43_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_44_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_45_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_46_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_47_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_48_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_49_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_50_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_51_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_52_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_53_SLEW" value="slow" />

|

||||

|

||||

<!--########################################################################

|

||||

# Enable USB Reset last

|

||||

########################################################################-->

|

||||

<user_parameter name="CONFIG.PCW_USB0_RESET_ENABLE" value="1" />

|

||||

|

||||

<!--########################################################################

|

||||

# Extra stuff?

|

||||

########################################################################-->

|

||||

<user_parameter name="CONFIG.PCW_USE_S_AXI_HP0" value="1" />

|

||||

<user_parameter name="CONFIG.PCW_IRQ_F2P_INTR" value="1" />

|

||||

</user_parameters>

|

||||

</ip>

|

||||

</ip_preset>

|

||||

<ip_preset preset_proc_name="rgb_led_preset">

|

||||

<ip vendor="xilinx.com" library="ip" name="axi_gpio" ip_interface="GPIO">

|

||||

<user_parameters>

|

||||

<user_parameter name="CONFIG.C_GPIO_WIDTH" value="3"/>

|

||||

<user_parameter name="CONFIG.C_ALL_INPUTS" value="0"/>

|

||||

<user_parameter name="CONFIG.C_ALL_OUTPUTS" value="1"/>

|

||||

</user_parameters>

|

||||

</ip>

|

||||

<ip vendor="xilinx.com" library="ip" name="axi_gpio" ip_interface="GPIO2">

|

||||

<user_parameters>

|

||||

<user_parameter name="CONFIG.C_IS_DUAL" value="1"/>

|

||||

<user_parameter name="CONFIG.C_GPIO2_WIDTH" value="3"/>

|

||||

<user_parameter name="CONFIG.C_ALL_OUTPUTS_2" value="1"/>

|

||||

<user_parameter name="CONFIG.C_ALL_INPUTS_2" value="0"/>

|

||||

</user_parameters>

|

||||

</ip>

|

||||

</ip_preset>

|

||||

<ip_preset preset_proc_name="buzzer_preset">

|

||||

<ip vendor="xilinx.com" library="ip" name="axi_gpio" ip_interface="GPIO">

|

||||

<user_parameters>

|

||||

<user_parameter name="CONFIG.C_GPIO_WIDTH" value="1"/>

|

||||

<user_parameter name="CONFIG.C_ALL_INPUTS" value="0"/>

|

||||

<user_parameter name="CONFIG.C_ALL_OUTPUTS" value="1"/>

|

||||

</user_parameters>

|

||||

</ip>

|

||||

<ip vendor="xilinx.com" library="ip" name="axi_gpio" ip_interface="GPIO2">

|

||||

<user_parameters>

|

||||

<user_parameter name="CONFIG.C_IS_DUAL" value="1"/>

|

||||

<user_parameter name="CONFIG.C_GPIO2_WIDTH" value="1"/>

|

||||

<user_parameter name="CONFIG.C_ALL_OUTPUTS_2" value="1"/>

|

||||

<user_parameter name="CONFIG.C_ALL_INPUTS_2" value="0"/>

|

||||

</user_parameters>

|

||||

</ip>

|

||||

</ip_preset>

|

||||

<ip_preset preset_proc_name="sws_4bits_preset">

|

||||

<ip vendor="xilinx.com" library="ip" name="axi_gpio" ip_interface="GPIO">

|

||||

<user_parameters>

|

||||

<user_parameter name="CONFIG.C_GPIO_WIDTH" value="4"/>

|

||||

<user_parameter name="CONFIG.C_ALL_INPUTS" value="1"/>

|

||||

<user_parameter name="CONFIG.C_ALL_OUTPUTS" value="0"/>

|

||||

</user_parameters>

|

||||

</ip>

|

||||

<ip vendor="xilinx.com" library="ip" name="axi_gpio" ip_interface="GPIO2">

|

||||

<user_parameters>

|

||||

<user_parameter name="CONFIG.C_IS_DUAL" value="1"/>

|

||||

<user_parameter name="CONFIG.C_GPIO2_WIDTH" value="4"/>

|

||||

<user_parameter name="CONFIG.C_ALL_OUTPUTS_2" value="0"/>

|

||||

<user_parameter name="CONFIG.C_ALL_INPUTS_2" value="1"/>

|

||||

</user_parameters>

|

||||

</ip>

|

||||

</ip_preset>

|

||||

</ip_presets>

|

||||

BIN

boards/board_files/zturn-7z010/2.1/zturn_board.jpg

Normal file

BIN

boards/board_files/zturn-7z010/2.1/zturn_board.jpg

Normal file

Binary file not shown.

|

After Width: | Height: | Size: 219 KiB |

141

boards/board_files/zturn-7z020/2.1/board.xml

Normal file

141

boards/board_files/zturn-7z020/2.1/board.xml

Normal file

|

|

@ -0,0 +1,141 @@

|

|||

<?xml version="1.0" encoding="UTF-8" standalone="no" ?><!--

|

||||

################################################################################

|

||||

#

|

||||

# MYiR Z-turn Board Definition File

|

||||

#

|

||||

# Sergiusz 'q3k' Bazański <q3k@q3k.org>

|

||||

# Steffen 'stv0g' Vogel <stv0g@0l.de>

|

||||

#

|

||||

################################################################################-->

|

||||

|

||||

<board name="mys-7z020" schema_version="2.1" vendor="myir.com" display_name="Z-turn Board (MYS-7Z020-C)" url="http://www.myirtech.com/list.asp?id=502" preset_file="preset.xml">

|

||||

<images>

|

||||

<image name="zturn_board.jpg" display_name="Z-turn Board" sub_type="board">

|

||||

<description>Z-turn Board top image</description>

|

||||

</image>

|

||||

</images>

|

||||

<description>The Z-turn board is a cheap Zynq evaluation board from the Chinese company MYiR Technologies.</description>

|

||||

<file_version>2.1</file_version>

|

||||

<compatible_board_revisions>

|

||||

<revision id="0">4</revision>

|

||||

</compatible_board_revisions>

|

||||

<components>

|

||||

<component name="part0" display_name="Z-turn Board" type="fpga" part_name="xc7z020clg400-1" pin_map_file="part0_pins.xml" vendor="xilinx" spec_url="http://www.myirtech.com/list.asp?id=502">

|

||||

<description>FPGA part on the board</description>

|

||||

<interfaces>

|

||||

<interface name="ps7_fixedio" mode="master" type="xilinx.com:display_processing_system7:fixedio_rtl:1.0" of_component="ps7_fixedio" preset_proc="ps7_preset" />

|

||||

<interface name="rgb_led" mode="master" type="xilinx.com:interface:gpio_rtl:1.0" of_component="rgb_led" preset_proc="rgb_led_preset">

|

||||

<preferred_ips>

|

||||

<preferred_ip name="axi_gpio" vendor="xilinx.com" library="ip" order="0" />

|

||||

</preferred_ips>

|

||||

<port_maps>

|

||||

<port_map logical_port="TRI_O" physical_port="rgb_led_tri_o" dir="out" left="2" right="0">

|

||||

<pin_maps>

|

||||

<pin_map port_index="0" component_pin="rgb_led_tri_o_0" />

|

||||

<pin_map port_index="1" component_pin="rgb_led_tri_o_1" />

|

||||

<pin_map port_index="2" component_pin="rgb_led_tri_o_2" />

|

||||

</pin_maps>

|

||||

</port_map>

|

||||

</port_maps>

|

||||

</interface>

|

||||

<interface name="buzzer" mode="master" type="xilinx.com:interface:gpio_rtl:1.0" of_component="buzzer" preset_proc="buzzer_preset">

|

||||

<preferred_ips>

|

||||

<preferred_ip name="axi_gpio" vendor="xilinx.com" library="ip" order="0" />

|

||||

</preferred_ips>

|

||||

<port_maps>

|

||||

<port_map logical_port="TRI_O" physical_port="buzzer_tri_o" dir="out">

|

||||

<pin_maps>

|

||||

<pin_map port_index="0" component_pin="buzzer_tri_o_0" />

|

||||

</pin_maps>

|

||||

</port_map>

|

||||

</port_maps>

|

||||

</interface>

|

||||

<interface name="sws_4bits" mode="master" type="xilinx.com:interface:gpio_rtl:1.0" of_component="sws_4bits" preset_proc="sws_4bits_preset">

|

||||

<preferred_ips>

|

||||

<preferred_ip vendor="xilinx.com" library="ip" name="axi_gpio" order="0" />

|

||||

</preferred_ips>

|

||||

<port_maps>

|

||||

<port_map logical_port="TRI_I" physical_port="sws_4bits_tri_i" dir="in" left="3" right="0">

|

||||

<pin_maps>

|

||||

<pin_map port_index="0" component_pin="sws_4bits_tri_i_0" />

|

||||

<pin_map port_index="1" component_pin="sws_4bits_tri_i_1" />

|

||||

<pin_map port_index="2" component_pin="sws_4bits_tri_i_2" />

|

||||

<pin_map port_index="3" component_pin="sws_4bits_tri_i_3" />

|

||||

</pin_maps>

|

||||

</port_map>

|

||||

</port_maps>

|

||||

</interface>

|

||||

<interface mode="master" name="i2c0" type="xilinx.com:interface:iic_rtl:1.0" of_component="i2c0">

|

||||

<description>I2C Interface for onboard G-rate and temperature sensors</description>

|

||||

<preferred_ips>

|

||||

<preferred_ip vendor="xilinx.com" library="ip" name="axi_iic" order="0" />

|

||||

</preferred_ips>

|

||||

<port_maps>

|

||||

<port_map logical_port="SDA_I" physical_port="i2c0_sda_i" dir="in">

|

||||

<pin_maps>

|

||||

<pin_map port_index="0" component_pin="i2c0_sda_i" />

|

||||

</pin_maps>

|

||||

</port_map>

|

||||

<port_map logical_port="SDA_O" physical_port="i2c0_sda_o" dir="out">

|

||||

<pin_maps>

|

||||

<pin_map port_index="0" component_pin="i2c0_sda_i" />

|

||||

</pin_maps>

|

||||

</port_map>

|

||||

<port_map logical_port="SDA_T" physical_port="i2c0_sda_t" dir="out">

|

||||

<pin_maps>

|

||||

<pin_map port_index="0" component_pin="i2c0_sda_i" />

|

||||

</pin_maps>

|

||||

</port_map>

|

||||

<port_map logical_port="SCL_I" physical_port="i2c0_scl_i" dir="in">

|

||||

<pin_maps>

|

||||

<pin_map port_index="0" component_pin="i2c0_scl_i" />

|

||||

</pin_maps>

|

||||

</port_map>

|

||||

<port_map logical_port="SCL_O" physical_port="i2c0_scl_o" dir="out">

|

||||

<pin_maps>

|

||||

<pin_map port_index="0" component_pin="i2c0_scl_i" />

|

||||

</pin_maps>

|

||||

</port_map>

|

||||

<port_map logical_port="SCL_T" physical_port="i2c0_scl_t" dir="out">

|

||||

<pin_maps>

|

||||

<pin_map port_index="0" component_pin="i2c0_scl_i" />

|

||||

</pin_maps>

|

||||

</port_map>

|

||||

</port_maps>

|

||||

</interface>

|

||||

</interfaces>

|

||||

</component>

|

||||

<component name="ps7_fixedio" display_name="PS7 fixed IO" type="chip" sub_type="fixed_io" major_group="" />

|

||||

<component name="buzzer" display_name="Piezo Buzzer" type="chip" sub_type="led" major_group="General Purpose Input or Output">

|

||||

<description>Piezo Buzzer on Board (Schematic: M1)</description>

|

||||

</component>

|

||||

<component name="rgb_led" display_name="RGB LED" type="chip" sub_type="led" major_group="General Purpose Input or Output">

|

||||

<description>RGB LED, 2 to 0, Active Low (Schematic: D34)</description>

|

||||

</component>

|

||||

<component name="sws_4bits" display_name="DIP switches" type="chip" sub_type="switch" major_group="General Purpose Input or Output">

|

||||

<description>DIP Switches, 3 to 0 (Schematic: U20)</description>

|

||||

</component>

|

||||

<component name="i2c0" display_name="IIC" type="chip" sub_type="mux" major_group="Miscellaneous">

|

||||

<description>I2C Bus 0 wired to PL</description>

|

||||

</component>

|

||||

</components>

|

||||

<jtag_chains>

|

||||

<jtag_chain name="chain1">

|

||||

<position name="0" component="part0" />

|

||||

</jtag_chain>

|

||||

</jtag_chains>

|

||||

<connections>

|

||||

<connection name="part0_rgb_led" component1="part0" component2="rgb_led">

|

||||

<connection_map name="part0_rgb_led_1" c1_st_index="4" c1_end_index="6" c2_st_index="0" c2_end_index="2" />

|

||||

</connection>

|

||||

<connection name="part0_sws_4bits" component1="part0" component2="sws_4bits">

|

||||

<connection_map name="part0_sws_4bits_1" c1_st_index="0" c1_end_index="3" c2_st_index="0" c2_end_index="3" />

|

||||

</connection>

|

||||

<connection name="part0_buzzer" component1="part0" component2="buzzer">

|

||||

<connection_map name="part0_buzzer_1" c1_st_index="7" c1_end_index="7" c2_st_index="0" c2_end_index="0" />

|

||||

</connection>

|

||||

<connection name="part0_i2c0" component1="part0" component2="i2c0">

|

||||

<connection_map name="part0_i2c0_1" c1_st_index="8" c1_end_index="9" c2_st_index="0" c2_end_index="1" />

|

||||

</connection>

|

||||

</connections>

|

||||

</board>

|

||||

26

boards/board_files/zturn-7z020/2.1/part0_pins.xml

Normal file

26

boards/board_files/zturn-7z020/2.1/part0_pins.xml

Normal file

|

|

@ -0,0 +1,26 @@

|

|||

<?xml version="1.0" encoding="UTF-8" standalone="no"?><!--

|

||||

################################################################################

|

||||

#

|

||||

# MYiR Z-turn FPGA Pin Definition File

|

||||

#

|

||||

# Sergiusz 'q3k' Bazański <q3k@q3k.org>

|

||||

# Steffen 'stv0g' Vogel <stv0g@0l.de>

|

||||

#

|

||||

################################################################################-->

|

||||

|

||||

<part_info part_name="xc7z020clg400-1">

|

||||

<pins>

|

||||

<pin index="0" name="sws_4bits_tri_i_0" iostandard="LVCMOS33" loc="R19" /><!-- IO_B34_0 -->

|

||||

<pin index="1" name="sws_4bits_tri_i_1" iostandard="LVCMOS33" loc="T19" /><!-- IO_B34_25 -->

|

||||

<pin index="2" name="sws_4bits_tri_i_2" iostandard="LVCMOS33" loc="G14" /><!-- IO_B35_0 -->

|

||||

<pin index="3" name="sws_4bits_tri_i_3" iostandard="LVCMOS33" loc="J15" /><!-- IO_B35_25 -->

|

||||

<pin index="4" name="rgb_led_tri_o_0" iostandard="LVCMOS33" loc="R14" /><!-- IO_B34_LN6 -->

|

||||

<pin index="5" name="rgb_led_tri_o_1" iostandard="LVCMOS33" loc="Y16" /><!-- IO_B34_LP7 -->

|

||||

<pin index="6" name="rgb_led_tri_o_2" iostandard="LVCMOS33" loc="Y17" /><!-- IO_B34_LN7 -->

|

||||

<pin index="7" name="buzzer_tri_o_0" iostandard="LVCMOS33" loc="P18" /><!-- BP -->

|

||||

<pin index="8" name ="i2c0_scl_i" iostandard="LVCMOS33" loc="P16" /><!-- I2C0_SCL -->

|

||||

<pin index="9" name ="i2c0_sda_i" iostandard="LVCMOS33" loc="P15" /><!-- I2C0_SDA -->

|

||||

<pin index="10" name="mems_temp_intn" iostandard="LVCMOS33" loc="N17" /><!-- MEMS_INTn (wired-or for LM75 and Sil902x)-->

|

||||

<pin index="11" name="hdmi_int" iostandard="LVCMOS33" loc="W19" /><!-- HDMI_INT -->

|

||||

</pins>

|

||||

</part_info>

|

||||

324

boards/board_files/zturn-7z020/2.1/preset.xml

Normal file

324

boards/board_files/zturn-7z020/2.1/preset.xml

Normal file

|

|

@ -0,0 +1,324 @@

|

|||

<?xml version="1.0" encoding="UTF-8" standalone="no" ?><!--

|

||||

################################################################################

|

||||

#

|

||||

# MYiR Z-turn Board IP Presets

|

||||

#

|

||||

# Sergiusz 'q3k' Bazański <q3k@q3k.org>

|

||||

# Steffen 'stv0g' Vogel <stv0g@0l.de>

|

||||

#

|

||||

################################################################################-->

|

||||

|

||||

<ip_presets schema="1.0">

|

||||

<ip_preset preset_proc_name="ps7_preset">

|

||||

<ip vendor="xilinx.com" library="ip" name="processing_system7" version="*">

|

||||

<user_parameters>

|

||||

<!--########################################################################

|

||||

# PS Bank Voltage, Busses, Clocks

|

||||

########################################################################-->

|

||||

<user_parameter name="CONFIG.PCW_PRESET_BANK0_VOLTAGE" value="LVCMOS 3.3V" />

|

||||

<user_parameter name="CONFIG.PCW_PRESET_BANK1_VOLTAGE" value="LVCMOS 1.8V" />

|

||||

<user_parameter name="CONFIG.PCW_PACKAGE_NAME" value="clg400" />

|

||||

<user_parameter name="CONFIG.PCW_USE_M_AXI_GP0" value="1" />

|

||||

<user_parameter name="CONFIG.PCW_USE_M_AXI_GP1" value="0" />

|

||||

<user_parameter name="CONFIG.PCW_CRYSTAL_PERIPHERAL_FREQMHZ" value="33.333333" />

|

||||

<user_parameter name="CONFIG.PCW_ARMPLL_CTRL_FBDIV" value="40" />

|

||||

<user_parameter name="CONFIG.PCW_APU_CLK_RATIO_ENABLE" value="6:2:1" />

|

||||

<user_parameter name="CONFIG.PCW_CPU_PERIPHERAL_CLKSRC" value="ARM PLL" />

|

||||

<user_parameter name="CONFIG.PCW_DDR_PERIPHERAL_CLKSRC" value="DDR PLL" />

|

||||

<user_parameter name="CONFIG.PCW_QSPI_PERIPHERAL_CLKSRC" value="IO PLL" />

|

||||

<user_parameter name="CONFIG.PCW_ENET0_PERIPHERAL_CLKSRC" value="ARM PLL" />

|

||||

<user_parameter name="CONFIG.PCW_SDIO_PERIPHERAL_CLKSRC" value="IO PLL" />

|

||||

<user_parameter name="CONFIG.PCW_UART_PERIPHERAL_CLKSRC" value="IO PLL" />

|

||||

<user_parameter name="CONFIG.PCW_TTC0_CLK0_PERIPHERAL_CLKSRC" value="CPU_1X" />

|

||||

<user_parameter name="CONFIG.PCW_TTC0_CLK1_PERIPHERAL_CLKSRC" value="CPU_1X" />

|

||||

<user_parameter name="CONFIG.PCW_TTC0_CLK2_PERIPHERAL_CLKSRC" value="CPU_1X" />

|

||||

<user_parameter name="CONFIG.PCW_APU_PERIPHERAL_FREQMHZ" value="666.666666" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_ACT_DDR_FREQ_MHZ" value="533.333333" />

|

||||

<user_parameter name="CONFIG.PCW_ENET0_PERIPHERAL_FREQMHZ" value="1000 Mbps" />

|

||||

<user_parameter name="CONFIG.PCW_SDIO_PERIPHERAL_FREQMHZ" value="100" />

|

||||

<user_parameter name="CONFIG.PCW_QSPI_PERIPHERAL_FREQMHZ" value="200.000000" />

|

||||

<user_parameter name="CONFIG.PCW_UART_PERIPHERAL_FREQMHZ" value="100" />

|

||||

<user_parameter name="CONFIG.PCW_USB0_PERIPHERAL_FREQMHZ" value="60" />

|

||||

<user_parameter name="CONFIG.PCW_TTC0_CLK0_PERIPHERAL_FREQMHZ" value="133.333333" />

|

||||

<user_parameter name="CONFIG.PCW_TTC0_CLK1_PERIPHERAL_FREQMHZ" value="133.333333" />

|

||||

<user_parameter name="CONFIG.PCW_TTC0_CLK2_PERIPHERAL_FREQMHZ" value="133.333333" />

|

||||

|

||||

<!--########################################################################

|

||||

# Fabric Clocks - CLK0 enabled, CLK[3:1] disabled by default

|

||||

########################################################################-->

|

||||

<user_parameter name="CONFIG.PCW_FCLK0_PERIPHERAL_CLKSRC" value="IO PLL" />

|

||||

<user_parameter name="CONFIG.PCW_FCLK1_PERIPHERAL_CLKSRC" value="IO PLL" />

|

||||

<user_parameter name="CONFIG.PCW_FCLK2_PERIPHERAL_CLKSRC" value="IO PLL" />

|

||||

<user_parameter name="CONFIG.PCW_FCLK3_PERIPHERAL_CLKSRC" value="IO PLL" />

|

||||

<user_parameter name="CONFIG.PCW_FCLK_CLK0_BUF" value="true" />

|

||||

<user_parameter name="CONFIG.PCW_FCLK_CLK1_BUF" value="true" />

|

||||

<user_parameter name="CONFIG.PCW_FCLK_CLK2_BUF" value="false" />

|

||||

<user_parameter name="CONFIG.PCW_FCLK_CLK3_BUF" value="false" />

|

||||

<user_parameter name="CONFIG.PCW_FPGA0_PERIPHERAL_FREQMHZ" value="100" />

|

||||

<user_parameter name="CONFIG.PCW_FPGA1_PERIPHERAL_FREQMHZ" value="50" />

|

||||

<user_parameter name="CONFIG.PCW_FPGA2_PERIPHERAL_FREQMHZ" value="50" />

|

||||

<user_parameter name="CONFIG.PCW_FPGA3_PERIPHERAL_FREQMHZ" value="50" />

|

||||

<user_parameter name="CONFIG.PCW_EN_CLK0_PORT" value="1" />

|

||||

<user_parameter name="CONFIG.PCW_EN_CLK1_PORT" value="1" />

|

||||

<user_parameter name="CONFIG.PCW_EN_CLK2_PORT" value="0" />

|

||||

<user_parameter name="CONFIG.PCW_EN_CLK3_PORT" value="0" />

|

||||

<user_parameter name="CONFIG.PCW_EN_RST0_PORT" value="1" />

|

||||

<user_parameter name="CONFIG.PCW_EN_RST1_PORT" value="0" />

|

||||

<user_parameter name="CONFIG.PCW_EN_RST2_PORT" value="0" />

|

||||

<user_parameter name="CONFIG.PCW_EN_RST3_PORT" value="0" />

|

||||

|

||||

<!--########################################################################

|

||||

# DDR3

|

||||

########################################################################-->

|

||||

<user_parameter name="CONFIG.PCW_EN_DDR" value="1" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_PARTNO" value="MT41J256M16 RE-125" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_DEVICE_CAPACITY" value="4096 MBits" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_T_FAW" value="40.0" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_T_RC" value="48.91" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_CWL" value="6" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_DRAM_WIDTH" value="16 Bits" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_T_RAS_MIN" value="35.0" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_SPEED_BIN" value="DDR3_1066F" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_CLOCK_0_LENGTH_MM" value="0" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_CLOCK_1_LENGTH_MM" value="0" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_CLOCK_2_LENGTH_MM" value="0" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_CLOCK_3_LENGTH_MM" value="0" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_DQ_0_LENGTH_MM" value="0" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_DQ_1_LENGTH_MM" value="0" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_DQ_2_LENGTH_MM" value="0" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_DQ_3_LENGTH_MM" value="0" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_DQS_0_LENGTH_MM" value="0" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_DQS_1_LENGTH_MM" value="0" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_DQS_2_LENGTH_MM" value="0" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_DQS_3_LENGTH_MM" value="0" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_TRAIN_DATA_EYE" value="1" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_TRAIN_WRITE_LEVEL" value="1" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_TRAIN_READ_GATE" value="1" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_DQS_TO_CLK_DELAY_0" value="0.229" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_DQS_TO_CLK_DELAY_1" value="0.250" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_DQS_TO_CLK_DELAY_2" value="0.121" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_DQS_TO_CLK_DELAY_3" value="0.146" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_BOARD_DELAY0" value="0.271" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_BOARD_DELAY1" value="0.259" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_BOARD_DELAY2" value="0.219" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_BOARD_DELAY3" value="0.207" />

|

||||

<user_parameter name="CONFIG.PCW_UIPARAM_DDR_USE_INTERNAL_VREF" value="0" />

|

||||

|

||||

<!--########################################################################

|

||||

# Peripheral assignments

|

||||

########################################################################-->

|

||||

<user_parameter name="CONFIG.PCW_QSPI_GRP_SINGLE_SS_IO" value="MIO 1 .. 6" />

|

||||

<user_parameter name="CONFIG.PCW_USB0_RESET_IO" value="MIO 7" />

|

||||

<user_parameter name="CONFIG.PCW_QSPI_GRP_FBCLK_IO" value="MIO 8" />

|

||||

<user_parameter name="CONFIG.PCW_UART0_UART0_IO" value="MIO 10 .. 11" />

|

||||

<user_parameter name="CONFIG.PCW_I2C0_I2C0_IO" value="EMIO" />

|

||||

<user_parameter name="CONFIG.PCW_I2C1_I2C1_IO" value="MIO 12 .. 13" />

|

||||

<user_parameter name="CONFIG.PCW_CAN0_CAN0_IO" value="MIO 14 .. 15" />

|

||||

<user_parameter name="CONFIG.PCW_ENET0_ENET0_IO" value="MIO 16 .. 27" />

|

||||

<user_parameter name="CONFIG.PCW_USB0_USB0_IO" value="MIO 28 .. 39" />

|

||||

<user_parameter name="CONFIG.PCW_SD0_SD0_IO" value="MIO 40 .. 45" />

|

||||

<user_parameter name="CONFIG.PCW_SD0_GRP_CD_IO" value="MIO 46" />

|

||||

<user_parameter name="CONFIG.PCW_SD0_GRP_WP_IO" value="MIO 47" />

|

||||

<user_parameter name="CONFIG.PCW_UART1_UART1_IO" value="MIO 48 .. 49" />

|

||||

<user_parameter name="CONFIG.PCW_ENET0_GRP_MDIO_IO" value="MIO 52 .. 53" />

|

||||

<user_parameter name="CONFIG.PCW_TTC0_TTC0_IO" value="EMIO" />

|

||||

|

||||

<!--########################################################################

|

||||

# Enable Peripherals

|

||||

########################################################################-->

|

||||

<user_parameter name="CONFIG.PCW_QSPI_PERIPHERAL_ENABLE" value="1" />

|

||||

<user_parameter name="CONFIG.PCW_QSPI_GRP_FBCLK_ENABLE" value="1" />

|

||||

<user_parameter name="CONFIG.PCW_QSPI_GRP_SINGLE_SS_ENABLE" value="1" />

|

||||

<user_parameter name="CONFIG.PCW_USB0_PERIPHERAL_ENABLE" value="1" />

|

||||

<user_parameter name="CONFIG.PCW_ENET0_PERIPHERAL_ENABLE" value="1" />

|

||||

<user_parameter name="CONFIG.PCW_ENET0_GRP_MDIO_ENABLE" value="1" />

|

||||

<user_parameter name="CONFIG.PCW_SD0_PERIPHERAL_ENABLE" value="1" />

|

||||

<user_parameter name="CONFIG.PCW_SD0_GRP_CD_ENABLE" value="1" />

|

||||

<user_parameter name="CONFIG.PCW_SD0_GRP_WP_ENABLE" value="1" />

|

||||

<user_parameter name="CONFIG.PCW_CAN0_PERIPHERAL_ENABLE" value="1" />

|

||||

<user_parameter name="CONFIG.PCW_I2C0_PERIPHERAL_ENABLE" value="1" />

|

||||

<user_parameter name="CONFIG.PCW_I2C1_PERIPHERAL_ENABLE" value="1" />

|

||||

<user_parameter name="CONFIG.PCW_UART0_PERIPHERAL_ENABLE" value="1" />

|

||||

<user_parameter name="CONFIG.PCW_UART1_PERIPHERAL_ENABLE" value="1" />

|

||||

<user_parameter name="CONFIG.PCW_GPIO_PERIPHERAL_ENABLE" value="1" />

|

||||

<user_parameter name="CONFIG.PCW_GPIO_MIO_GPIO_ENABLE" value="1" />

|

||||

<user_parameter name="CONFIG.PCW_GPIO_EMIO_GPIO_ENABLE" value="0" />

|

||||

<user_parameter name="CONFIG.PCW_TTC0_PERIPHERAL_ENABLE" value="1" />

|

||||

|

||||

<!--########################################################################

|

||||

# Configure MIOs

|

||||

########################################################################-->

|

||||

<user_parameter name="CONFIG.PCW_MIO_0_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_1_PULLUP" value="disabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_2_PULLUP" value="disabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_3_PULLUP" value="disabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_4_PULLUP" value="disabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_5_PULLUP" value="disabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_6_PULLUP" value="disabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_7_PULLUP" value="disabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_8_PULLUP" value="disabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_9_PULLUP" value="disabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_10_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_11_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_12_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_13_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_14_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_15_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_16_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_17_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_18_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_19_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_20_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_21_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_22_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_23_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_24_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_25_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_26_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_27_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_28_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_29_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_30_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_31_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_32_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_33_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_34_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_35_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_36_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_37_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_38_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_39_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_40_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_41_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_42_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_43_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_44_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_45_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_46_PULLUP" value="disabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_47_PULLUP" value="disabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_48_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_49_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_50_PULLUP" value="disabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_51_PULLUP" value="disabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_52_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_53_PULLUP" value="enabled" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_0_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_1_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_2_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_3_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_4_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_5_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_6_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_7_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_8_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_9_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_10_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_11_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_12_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_13_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_14_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_15_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_16_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_17_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_18_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_19_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_20_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_21_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_22_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_23_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_24_SLEW" value="slow" />

|

||||

<user_parameter name="CONFIG.PCW_MIO_25_SLEW" value="slow" />

|

||||